在電子產品設計中,PCB布局布線是最重要的一步,PCB布局布線的好壞將直接影響電路的性能。現在�����,雖然有很多軟件可以實現PCB自動布局布線����。但是隨著信號頻率不斷提升����,很多時候,工程師需要了解有關PCB布局布線的最基本的原則和技巧�����,才可以讓自己的設計完美無缺����。

接下來深圳PCB設計公司-深圳宏力捷電子以問答形式為大家解答電路板設計常見問題�����。

1、[問] 高頻信號布線時要注意哪些問題����?

[答 ]1.信號線的阻抗匹配;

2.與其他信號線的空間隔離����;

3.對于數字高頻信號,差分線效果會更好����;

2、[問] 在布板時�,如果線密,過孔就可能要多����,當然就會影響板子的電氣性能,請問怎樣提高板子的電氣性能����?

[答] 對于低頻信號,過孔不要緊���,高頻信號盡量減少過孔�����。如果線多可以考慮多層板��;

3��、[問] 是不是板子上加的去耦電容越多越好��?

[答] 去耦電容需要在合適的位置加合適的值�。例如,在你的模擬器件的供電端口就進加�����,并且需要用不同的電容值去濾除不同頻率的雜散信號�;

4、[問] 一個好的板子它的標準是什么�?

[答] 布局合理、功率線功率冗余度足夠�、高頻阻抗阻抗、低頻走線簡潔�。

5�����、[問] 通孔和盲孔對信號的差異影響有多大?應用的原則是什么�?

[答] 采用盲孔或埋孔是提高多層板密度、減少層數和板面尺寸的有效方法����,并大大減少了鍍覆通孔的數量。但相比較而言����,通孔在工藝上好實現,成本較低���,所以一般設計中都使用通孔��。

6����、[問] 在涉及模擬數字混合系統的時候���,有人建議電層分割�����,地平面采取整片敷銅�,也有人建議電地層都分割,不同的地在電源源端點接��,但是這樣對信號的回流路徑就遠了�����,具體應用時應如何選擇合適的方法�����?

[答] 如果你有高頻>20MHz信號線���,并且長度和數量都比較多�,那么需要至少兩層給這個模擬高頻信號���。一層信號線����、一層大面積地���,并且信號線層需要打足夠的過孔到地��。這樣的目的是:

1���、對于模擬信號,這提供了一個完整的傳輸介質和阻抗匹配�;

2、地平面把模擬信號和其他數字信號進行隔離�;

3、地回路足夠小�,因為你打了很多過孔,地有是一個大平面��。

7��、[問] 在電路板中�,信號輸入插件在PCB最左邊沿,mcu在靠右邊����,那么在布局時是把穩壓電源芯片放置在靠近接插件(電源IC輸出5V經過一段比較長的路徑才到達MCU),還是把電源IC放置到中間偏右(電源IC的輸出5V的線到達MCU就比較短�,但輸入電源線就經過比較長一段PCB板)?或是有更好的布局�?

[答] 首先你的所謂信號輸入插件是否是模擬器件?如果是是模擬器件�,建議你的電源布局應盡量不影響到模擬部分的信號完整性.因此有幾點需要考慮:

(1)首先你的穩壓電源芯片是否是比較干凈���,紋波小的電源.對模擬部分的供電,對電源的要求比較高.

(2)模擬部分和你的MCU是否是一個電源�����,在高精度電路的設計中����,建議把模擬部分和數字部分的電源分開.

(3)對數字部分的供電需要考慮到盡量減小對模擬電路部分的影響.

8、[問] 在高速信號鏈的應用中�����,對于多ASIC都存在模擬地和數字地���,究竟是采用地分割�����,還是不分割地��?既有準則是什么�?哪種效果更好?

[答] 迄今為止�,沒有定論。一般情況下你可以查閱芯片的手冊�����。ADI所有混合芯片的手冊中都是推薦你一種接地的方案�����,有些是推薦公地�����、有些是建議隔離地�。這取決于芯片設計�。

9、[問] 何時要考慮線的等長��?如果要考慮使用等長線的話�����,兩根信號線之間的長度之差最大不能超過多少����?如何計算�����?

[答] 差分線計算思路:如果你傳一個正弦信號���,你的長度差等于它傳輸波長的一半是,相位差就是180度�����,這時兩個信號就完全抵消了���。所以這時的長度差是最大值��。以此類推�����,信號線差值一定要小于這個值���。

10、[問] 高速中的蛇形走線���,適合在那種情況��?有什么缺點沒��,比如對于差分走線���,又要求兩組信號是正交的����?

[答] 蛇形走線�����,因為應用場合不同而具不同的作用:

(1)如果蛇形走線在計算機板中出現����,其主要起到一個濾波電感和阻抗匹配的作用��,提高電路的抗干擾能力����。計算機主機板中的蛇形走線,主要用在一些時鐘信號中����,如PCI-Clk,AGPCIK,IDE,DIMM等信號線����。

(2)若在一般普通PCB板中�����,除了具有濾波電感的作用外����,還可作為收音機天線的電感線圈等等。如2.4G的對講機中就用作電感�����。

(3)對一些信號布線長度要求必須嚴格等長�����,高速數字PCB板的等線長是為了使各信號的延遲差保持在一個范圍內��,保證系統在同一周期內讀取的數據的有效性(延遲差超過一個時鐘周期時會錯讀下一周期的數據)���。

(4)蛇形走線在某些特殊的電路中起到一個分布參數的LC濾波器的作用�。

11、[問]在設計PCB時�,如何考慮電磁兼容性EMC/EMI,具體需要考慮哪些方面��?采取哪些措施���?

[答] 好的EMI/EMC 設計必須一開始布局時就要考慮到器件的位置, PCB 疊層的安排�,重要聯機的走法����, 器件的選擇等。

例如時鐘產生器的位置盡量不要靠近對外的連接器���,高速信號盡量走內層并注意特性阻抗匹配與參考層的連續以減少反射��,器件所推的信號之斜率(slew rate)盡量小以減低高頻成分,選擇去耦合(decoupling/bypass)電容時注意其頻率響應是否符合需求以降低電源層噪聲���。另外���,注意高頻信號電流之回流路徑使其回路面積盡量小(也就是回路阻抗loop impedance 盡量小)以減少輻射, 還可以用分割地層的方式以控制高頻噪聲的范圍���,最后��,適當的選擇PCB 與外殼的接地點

12�、[問] 請問射頻寬帶電路PCB的傳輸線設計有何需要注意的地方?傳輸線的地孔如何設置比較合適�,阻抗匹配是需要自己設計還是要和PCB加工廠家合作?

[答] 這個問題要考慮很多因素.比如PCB材料的各種參數�����,根據這些參數最后建立的傳輸線模型���,器件的參數等.阻抗匹配一般要根據廠家提供的資料來設計��。

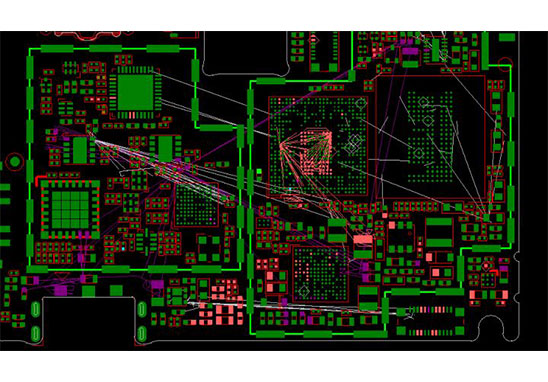

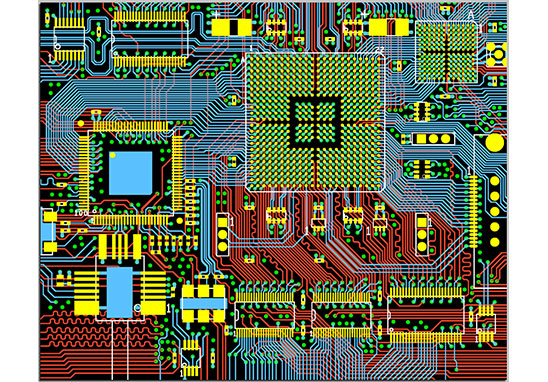

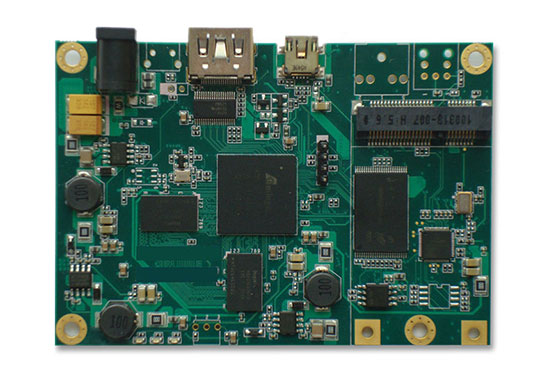

深圳宏力捷電子電路板設計能力:

最高信號設計速率:10Gbps CML差分信號����;

最高PCB設計層數:40層��;

最小線寬:2.4mil�;

最小線間距:2.4mil;

最小BGA PIN 間距:0.4mm��;

最小機械孔直徑:6mil�����;

最小激光鉆孔直徑:4mil;

最大PIN數目:����;63000+

最大元件數目:3600;

最多BGA數目:48+�����。

深圳宏力捷推薦服務:PCB設計打樣 | PCB抄板打樣 | PCB打樣&批量生產 | PCBA代工代料